共封装光子(CPO)作为突破AI算力瓶颈的关键技术,通过将光引擎与芯片一体封装,大幅提升传输速率与能效,已成为超算与AI算力中心的核心发展方向。光子集成电路(PIC)作为CPO及传统光芯片封装中的功能载体,其性能直接影响系统表现。PIC晶圆级测试对CPO尤为重要,通过验证其稳定性、一致性和可靠性,为高效集成与良率提升奠定基础。当前,面对多物理场、高密度集成等挑战,晶圆测试仍缺乏系统化、高效、高精度的解决方案,成为制约CPO及高端PIC技术规模化应用的产业瓶颈,亟需突破。

一、PIC 晶圆测试的挑战

PIC 晶圆测试是确保PIC器件性能与可靠性的核心环节,旨在封装前识别和剔除性能不合格的芯片,避免为不良品支付昂贵的封装和测试成本,并为晶圆工艺改进和良率提升提供直接的、基础性的数据支持。与传统的电芯片测试和单PIC芯片相比,PIC晶圆测试在以下几个方面面临挑战。

1.光学对准精度要求极高

光信号的耦合效率高度依赖于光纤探针与波导端面之间在六个自由度(X、Y、Z 位移和 Rx、Ry、Rz 旋转)上的亚微米级精确对准,而且必须保证光信号耦合的高重复性。传统电学探针仅需垂直接触,而光学测试需以非正交角度逼近,对准过程复杂且易发生碰撞,对机械系统与控制算法提出了极高要求。

2.工艺变异引入测量干扰

在从单芯片研发扩展至整片晶圆测试时,硅厚度不均匀、刻蚀线宽波动、套刻误差以及晶圆翘曲等工艺变异成为不可忽视的因素。这些变异导致每个芯片的最佳耦合位置发生偏移。若测试系统无法自动识别并补偿这些偏差,将难以区分器件真实性能与耦合误差,从而导致良率误判。

3.多域系统集成与协同复杂

光学测试需整合高精度运动平台、光学探头、电学仪器、机器视觉与温控模块等多个子系统。各系统需在微秒级别实现硬件触发与数据同步。缺乏统一的软件架构与通信标准进一步增加了系统集成与后期维护的复杂度与成本。

4.测试吞吐量成为量产瓶颈

光学耦合是一个串行且耗时的过程。每个测试点均需进行光功率搜索与优化,传统手动或半自动方案每点耗时可达数分钟,无法满足量产对效率的要求。

5.校准依赖性强,重复性差

光学测试结果极易受环境扰动与机械重复性的影响,晶圆重复装卸会引入位姿偏差。若缺乏标准化校准流程(SoP),测试数据的可比性与可靠性将难以保证。

二、PIC 晶圆测试中的光学耦合方式与光探针类型

(一)光学耦合方式

PIC中光信号一般是水平传输的,在CPO等光引擎中,PIC与其他有源、无源器件的耦合也是水平耦合的。为了评估PIC中的光路功能和性能,PIC 晶圆测试中的光耦合主要包括表面耦合与边缘耦合两种方式,取决于材料平台与芯片结构。

- 表面耦合(基于衍射光栅的垂直耦合)

通过引入衍射光栅,将晶圆内水平传输的待测光信号转向90°,垂直于晶圆表面进行耦合。这种方式利用光栅的衍射效应,将周期性光栅制作于芯片表面波导上。在输入端口,入射光信号以垂直方式入射到晶圆表面,当满足相位匹配条件时,光可高效耦合入水平的光波导。在输出端口,水平光波导中的出射光信号通过衍射光栅后,实现垂直于晶圆表面输出。该方式在硅光与氮化硅平台上工艺成熟、应用广泛,测试系统实现相对比较容易,但其主要劣势在于:1)带宽受限与耦合损耗较大,提高带宽常需采用多光栅复用等复杂方案。2)耦合光栅占用晶圆面积带来一定的成本。3)在PIC芯片与其他光学元器件水平耦合时,需要通过刻蚀等工艺将相关的衍射光栅去除,以实现水平波导端面暴露,带来额外成本和性能精度误差。

- 边缘耦合

适用于波导端面暴露或嵌入深槽的结构(如 InP 边缘发射器或硅光倒锥结构)。入射光信号和出射光信号直接在波导端面与光探针阵列进行高精度耦合,由测试系统基于光探针的光信号进行测量。光探针一般通过抛光阵列光纤或 3D 打印微透镜等方式实现。这种方式与PIC与其他元器件的耦合方式一致,测试结果更加直接、准确。边缘耦合具有带宽高、损耗低的优势。边缘耦合的难点是如何实现精准的光探针对准和提高耦合效率。在晶圆层面实现边缘耦合还需要晶圆上在芯片输入/输出端面刻蚀深槽。

由于边缘耦合具有直接、准确、综合成本低等优点,且在晶圆上为芯片测试预刻蚀耦合槽成本不高,已成为高带宽 PIC 测试的主流趋势。

(二)光探针类型

常用的光探针主要有以下三类:

1.平面光波导(PLC) 探针

基于硅或氮化硅材料,将光路精确路由至芯片边缘,模场尺寸可与 PIC 波导匹配,易于实现高端口密度与并行测试,适用于大规模量产。但其制造成本高,需针对特定 PIC 布局定制,设计周期长,灵活性较差。

2. 3D 打印光学探针

利用双光子聚合技术,在光纤端面集成 TIR 反射镜和非球面透镜等微光学结构,可实现高效精准的边缘耦合。但其聚合物材料热稳定性较差,通道易发生漂移,限制了其在长期稳定性要求高的场景中的应用。

2.抛光光纤阵列单元(FAU)

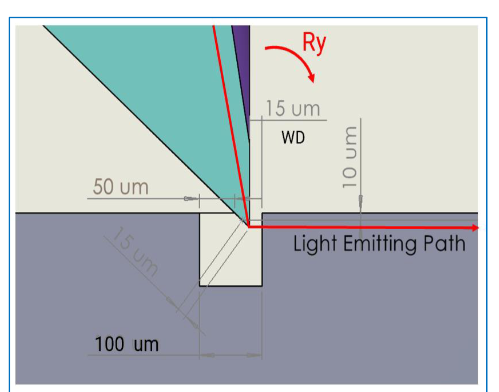

通过精密加工控制光纤端面的曲面形貌与光洁度,实现与纳米波导模场的最佳匹配,插入损耗极低。FAU 结构全玻璃/硅材质的热膨胀系数极小,在温度波动或机械应力下仍能保持稳定的光学性能。FAU的浅插入深度允许使用尺寸更小的耦合沟槽,可简化刻蚀工艺并降低成本,同时提升了自动化操作中的安全性,如图1。此外,设计测试平台需优化FAU角度,以确保安全插入沟槽、光路方向正确以及光纤通道与晶圆上的光端口精确对准。

三、Sunyu Photonics公司的系统性创新解决方案

晶圆级光子集成电路测试需要整合光学、电学和机械系统。多域的系统协同工作,是实现高效率、高可靠测试的关键所在。针对多领域协同带来的巨大挑战,Sunyu Photonics 公司推出了一套基于边缘耦合模式的高度集成、智能自动化的测试系统,显著提升了测试的重复性、吞吐量和可靠性,为PIC光子芯片的研发与量产提供了有力支撑。

1.应用于边缘耦合的抛光FAU的优化设计

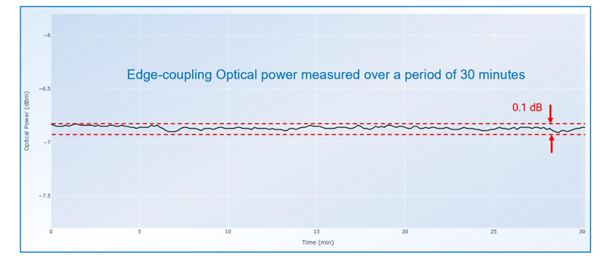

采用边缘耦合技术路线,充分发挥其高通真度、高带宽、低损耗的优势。采用自主优化的抛光FAU作为核心光学探头,其卓越的热机械稳定性(30分钟内光功率波动<0.1 dB,如图2所示)和可重复的耦合特性,为自动化量产测试奠定了坚实基础。

2.多层次全自动校准流程

校准是确保测试结果准确性的关键步骤。在晶圆级测试中,校准流程需要覆盖光学探针、运动平台和测试仪器等多个方面。通过精确的校准,可以消除系统误差,提高测试结果的可靠性和重复性。校准流程的设计和实施,是测试系统性能的重要保障。Sunyu Photonics集成了一套完善的校准流程,作为高重复性测试的基石。该校准流程保障了即使重新装片,测试差异仍可控制在 0.2 dB 以内。

校准流程通常包括顶相机校准、运动平台校准、晶圆校准和Z平面校准等步骤。顶相机校准用于确定全局坐标系和角度方向,确保机器视觉对准的准确性。运动平台校准则通过高精度定位技术,确保平台的位置精度。晶圆校准和Z平面校准则用于补偿晶圆表面的不平整,确保测试过程中的稳定对准。

1)视觉与运动基础校准:包括相机标定与平台定位精度校准(±1.5 μm),建立全局坐标系。

2)Z 轴平整度校准:通过采集多点构建晶圆表面三维高度图,实时补偿翘曲带来的 Z 向变化。

3)FAU 旋转中心(Pivot)校准:通过六轴操纵器进行小角度旋转并迭代计算,确定虚拟旋转中心,确保角度调整时不引起光纤末端的横向漂移,有效避免碰撞。

4)FAU 角度校准:依次校准插入角(Rz)、入射角(Ry)和阵列对齐角(Rx),确保光路正向耦合入波导。

全自动校准体系能有效补偿晶圆工艺变异和机械重复性误差,确保每次测试均在最佳状态下进行,小于0.1 dB次间(run-to-run)差异实现了极高的短期测试重复性,小于0.2 dB的装载间(load-to-load)差异则反映了系统长期重复性和鲁棒性以及软件算法、校准流程、自动化水平的综合实力。

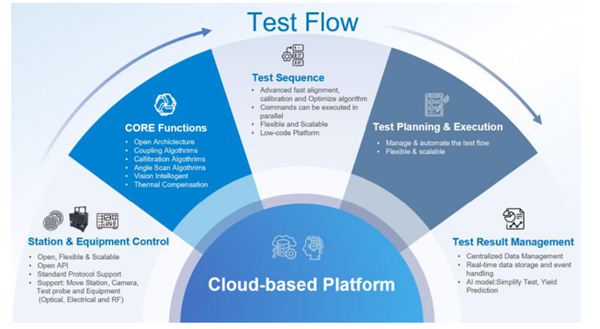

3.智能软件平台与高速算法

Navigo是Sunyu Photonics公司专有的PIC测试集成软件系统,专门设计应对自动化PIC集成光子晶圆测试中的多物理域参数交互及过程控制。Navigo无缝管理运动台、光学探针、电气仪器和视觉系统之间的复杂交互,确保在光学、电气、机械和热域之间协调操作,该软件平台构成整个自动化测试系统的“智能大脑”。其集成的高速梯度搜索算法,将光学对准时间缩短至3-4秒,彻底解决了边缘耦合的效率瓶颈。实测数据显示,系统可在125分钟内完成520个测试点,平均每点仅需14秒(包含平台移动、光纤对准和波长扫描),可显著提升PIC的量产效率UPH(每小时产量)。

1)低代码流程开发:通过图形化界面拖拽组件,工程师可快速构建包含波长扫描、偏振控制等复杂测试序列,显著降低开发门槛与时间成本。

2)实时数据处理与反馈:结合高速搜索与优化算法,系统能在毫秒级别完成光功率优化与数据采集,大幅提升测试吞吐量。

3)系统集成与通信控制:通过统一的软件架构协调多子系统运作,确保硬件触发与数据同步的高效与稳定。

Navigo模块化的可扩展软件平台专为实现复杂光子集成电路晶圆级测试而设计,测试流程如图3所示。

4.高稳定性硬件平台与自动化扩展

PS300测试平台提供亚微米级定位精度(<±1.5 µm)和高机械稳定性。可选配的全自动晶圆加载器,实现了无人化操作,杜绝人为误差,确保量产环境下的测试一致性与高效率。

光子集成电路(PIC)的晶圆级测试是一项涵盖精密机械、光学设计、自动控制与软件算法等多学科交叉的复杂系统工程。面对光学对准、工艺变异、系统集成、测试效率与重复性等核心挑战,Sunyu Photonics的解决方案直面PIC晶圆测试的核心痛点,通过光电软机一体化创新,成功破解了边缘耦合技术在精度、效率与可靠性方面的产业化难题,为PIC大规模量产提供了至关重要的测试保障,有望加速整个光子集成产业的发展进程。